[정의] 논리주소를 페이지 테이블을 이용하여 물리주소로 변경하여 메모리에 접근하는 방법

[논리주소] Process에서 사용하는 주소. Page number(p), page offset(d, 각 변수의 위치) 으로 구성

[물리주소] 실제 메인메모리를 frame 라고 하고 frame 위치에 저장된 주소

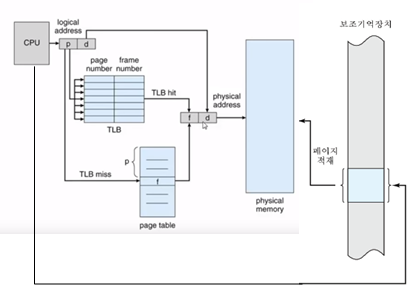

[변환방법] 그림참조

- 페이지 테이블에는 frame 번호가 저장.

[문제점] 페이지 테이블이 실제로 물리 메모리에 위치하고있어 두번 메모리 접근하여 성능 문제 발생

-> TBL를 이용하여 문제 해결 가능

[TLB] MMU 내부에 page table만 이용하는 공간 할당된 버퍼. Page table의 일부 내용만 저장.

[TLB 작동원리] 전체 검색후 윈하는 페이지를 찾고, 데이터의 위치를 찾음(P,D를 동시 저장).

- 전체 검색시에 검색시간 소요되므로, 전체를 비교가능한 캐시의 구조를 이용함.

[TLB를 이용한 주소변환] 그림참조

- TLB를 우선 찾고, TLB HIT 일때, 같이 저장된 frame을 가져와서 물리주소 구성

- TLB Miss 일때, Page table 찾아 물리주소 구성.

- TLB Miss 일때, 찾아온 물리주소를 새로 저장하기 위해 항목교체 알고리즘 필요

(LRU, FIFO, Random 등등)

- Process가 교체될때(문맥교환시) TLB 전체가 교체되어야함. 이럴때 Thrashing 발생가능하므로,

여러 Process의 내용을 동시에 보관하는 방법을 사용(Address-space Identifier(ASID))

[크기가 큰 페이지 테이블의 처리]

- 계층적 페이징, 해시 페이지 테이블, 역 페이지 테이블

'ITPE > CA_OS' 카테고리의 다른 글

| Hypervisor (0) | 2021.04.28 |

|---|---|

| Belady’s Anomaly (0) | 2021.04.28 |

| Cache Clean, Flush (0) | 2021.04.28 |

| MESI protocol (0) | 2021.04.28 |

| CPU 명령어 사이클 (0) | 2021.04.27 |